Home Search Collections Journals About Contact us My IOPscience

Electrical characteristics of silicon nanowire transistors fabricated by scanning probe and electron beam lithographies

This content has been downloaded from IOPscience. Please scroll down to see the full text. 2013 Nanotechnology 24 315205 (http://iopscience.iop.org/0957-4484/24/31/315205) View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 150.244.102.216 This content was downloaded on 19/11/2015 at 11:47

Please note that terms and conditions apply.

Nanotechnology **24** (2013) 315205 (7pp)

# Electrical characteristics of silicon nanowire transistors fabricated by scanning probe and electron beam lithographies

# Yu Kyoung Ryu, Marco Chiesa and Ricardo Garcia

Instituto de Ciencia de Materiales de Madrid, CSIC, Sor Juana Inés de la Cruz 3, E-28049 Madrid, Spain

#### E-mail: r.garcia@csic.es

Received 20 February 2013, in final form 24 May 2013 Published 15 July 2013 Online at stacks.iop.org/Nano/24/315205

#### Abstract

Silicon nanowire (SiNW) field-effect transistors have been fabricated by oxidation scanning probes and electron beam lithographies. The analysis and comparison of the electron mobility and subthreshold swing shows that the device performance is not affected by the top-down fabrication method. The two methods produce silicon nanowire transistors with similar electrical features, although oxidation scanning probe lithography generates nanowires with smaller channel widths. The values of the electron mobility and the subthreshold swing,  $200 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and  $500 \text{ mV} \text{ dec}^{-1}$ , respectively, are similar to those obtained from bottom-up methods. The compatibility of top-down methods with CMOS (complementary metal–oxide–semiconductor) procedures, the good electrical properties of the nanowire devices and the potential for making sub-10 nanowires, in particular by using oxidation scanning probe lithography, make those methods attractive for device fabrication.

(Some figures may appear in colour only in the online journal)

# 1. Introduction

Silicon nanowires with high surface-to-volume ratio are the building blocks of highly sensitive devices such as label-free biosensors [1–6], chemical sensors [7, 8], electromechanical resonators [9, 10] and photovoltaic devices [11, 12]. Silicon nanowires have also been applied to interface natural neuronal networks [13, 14]. Bottom-up and top-down approaches are currently used to fabricate silicon nanowire (SiNW) field-effect transistors. Bottom-up methods are based on catalyst-assisted growth [15]. Those methods are able to generate nanowires with diameters smaller than 5 nm. Top-down approaches are based on the use of lithographic methods such as electron beam lithography [16], and nanoimprint [17] and scanning probe lithography [18, 19]. In the context of nanowire transistors, Schottky barrier nanowire FETs are attractive because they avoid the use of dopants and parasitic resistances [20–23].

The high spatial resolution of the atomic force microscope (AFM) and its positioning capabilities make it possible to fabricate a silicon nanowire in a predefined region of a circuit. Scanning probe lithography (SPL) based on an oxidation process provides a precise control over the shape of the nanowire on a flat surface; thus, straight or curved nanowires have been fabricated [18]. Similarly, the beam positioning in an electron microscope allows contacting the nanowire to the external macroscopic electrodes. Thus both SPL and electron beam lithography are currently being developed to fabricate SiNW transistors. Furthermore, top-down lithographies are compatible with complementary metal-oxide-semiconductor (CMOS) technology which makes them convenient for integrating SiNW transistors with other devices. However, there are no comparisons of the advantages or disadvantages among the different top-down lithographies in terms of the SiNW electrical properties. Such observations, to a certain

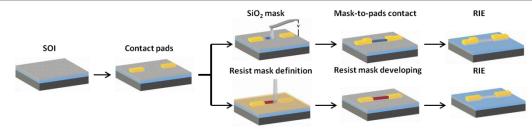

Figure 1. Scheme of the main SiNW fabrication steps in oxidation scanning probe lithography and electron beam lithography.

extent, also apply to other methods used to fabricate silicon nanowire devices.

Here, we apply two top-down nanolithographies [24-26]—oxidation scanning probe lithography (oSPL) and electron beam lithography (EBL)-to fabricate SiNW field-effect transistors. The two methods use as substrates chips cut from the same silicon-on-insulator wafer (SOI), which facilitates the direct comparison of the performance of the devices. In this study we measure the output and transfer characteristics of the SiNW FETs. From those curves, the electron mobility and subthreshold voltage can be deduced. Oxidation SPL and EBL have different fabrication steps; however, the electrical response of the transistors does not seem to be affected by the specific top-down fabrication method. The key factors that control the SiNW transistor properties are the size of the transistor channel and the electrical properties of the metal-nanowire contact at their interface. In this respect SPL and EBL produce channels of different sections, trapezoidal-like in oSPL and rectangular in EBL. In this study we have fabricated SiNWs with the full width at half-maximum (FWHM) being, respectively, 80 and 120 nm for SPL and EBL. The electron mobility and subthreshold swing are, respectively, 208 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 499 mV dec<sup>-1</sup> (SPL) and 200 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 537 mV dec $^{-1}$  (EBL). The electrical response of the devices improves significantly upon subjecting them to rapid thermal processing.

# 2. Nanofabrication methods

Figure 1 shows a scheme of the fabrication process for oSPL and EBL. The lithographies share several common elements: the SOI substrate, similar source and drain metal contacts and the removal of the unmasked regions of the top silicon layer by a reactive ion etching (RIE) system (PlasmaLab 80, Oxford Instruments, UK) with a plasma containing 20%  $O_2$  and 80% SF<sub>6</sub> with 8–12 s pulses. Furthermore, a key element of oSPL and EBL for fabricating SiNWs is the generation of a narrow mask for etching. The chemical nature of the mask depends on the lithography: a narrow silicon dioxide stripe in oSPL and a negative cross-linked resist stripe for EBL.

The SOI substrates have a 57 nm thick Si top layer with a nominal resistivity of  $\rho = 10-20 \ \Omega$  cm and a 151 nm thick buried oxide layer (SIMOX (separation by implantation of oxygen), IBIS Technology, Danvers, MA). The SOI was cleaned by sonication using a protocol of three cycles in NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (1:1:2) for 12 min each and a last cycle of 5 min in deionized water. A fresh NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O bath was used in each cycle. Then a photolithography step was performed to obtain the metal electrodes consisting of 5 nm of Cr and 40 nm of Au. Oxidation SPL is performed with a force microscope operated in the amplitude modulation mode [27, 28]. The AFM (Dimension V, Veeco, USA) was placed into a closed chamber to control the relative humidity. The oxidation was performed at a relative humidity of 60%. We have used n<sup>+</sup>-type doped silicon cantilevers (model NCHV, Bruker) with a force constant of about 42 N  $m^{-1}$  and a resonant frequency of 320 kHz. The cantilever was excited at its resonant frequency. Typical values of the parameters used to write the oxide lines are applied pulses of 15-30 V with ms duration. Following this step, the SiO<sub>2</sub> masks are contacted with the marker electrodes via another photolithography step. The above protocol yields silicon dioxide masks of 2-4 nm in thickness.

In electron beam lithography, the etch masks were obtained by writing lines over a layer of negative resist (AR-N 7500.08, Allresist GmbH, Strausberg, Germany) which was previously spin-coated and cured on the silicon top layer of the SOI, and developing them in the corresponding developer (AR 300-47, Allresist) to remove the unexposed areas of the resist.

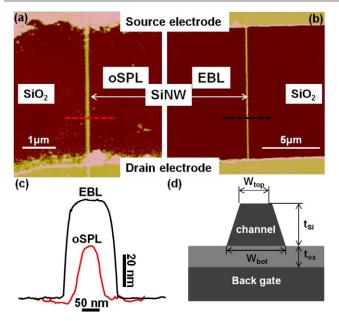

The last lithography step for both oSPL and EBL is the etching of the unmasked silicon by RIE. Figure 2 shows force microscopy images of a SiNW FET fabricated by oSPL (figure 2(a)) and EBL (figure 2(b)). For the two devices the electrical configuration is similar: a back-gated Schottky barrier field-effect transistor where the bridging nanowire between the source and drain electrodes acts as the transistor channel, the buried SiO<sub>2</sub> layer acting as the gate dielectric and the silicon substrate acting as a back gate.

The fabricated SiNWs were 5–10  $\mu$ m in length and 30–50 nm in thickness. The nanowire width depends on the lithography method; typical values of FWHM are 60–80 nm in SPL and 100–150 nm in EBL. The height of the fabricated nanowires is mostly determined by the original thickness of the silicon layer of the SOI although it may be reduced by the etching process. The fabricated SiNWs differ in shape. The nanowire cross-section is close to rectangular in EBL, while it is more trapezoidal-like in SPL, as a consequence of the mask shapes (figure 2(c)). In the case of oxidation SPL, the trapezoidal shape of the SiO<sub>2</sub> features is transferred to the silicon nanowire during the etching process, while the EBL method leads to more rectangular wires with quite steep walls. To make the comparison we have chosen SiNWs of

**Figure 2.** AFM images of two silicon nanowires. (a) Fabricated by oSPL. (b) Fabricated by EBL. (c) Cross-sections of the SiNWs marked in (a) and (b). (d) Cross-section scheme of a SiNW transistor.

comparable widths that correspond to nanowires of 80 nm (FWHM) for oSPL and 120 nm (FWHM) for EBL. However, the observed trends remain valid for the 11 SiNW FETs analyzed in this study.

The electrical properties of the devices have been measured as fabricated and after applying an annealing process consisting of a pulse of  $300 \,^{\circ}\text{C}$  for  $30 \,^{\circ}\text{S}$  in a N<sub>2</sub> atmosphere. The process was performed with a rapid thermal processing oven (Rapid Thermal Processor AS-Micro, Annealsys, France).

#### **3.** Electrical properties of the SiNW transistors

The common parameters for characterizing the electrical performance of a SiNW transistor are the threshold voltage  $(V_{\text{th}})$ , the subthreshold swing (SS), the on/off current ratio and the electron mobility. The first three parameters can be extracted directly from the transfer curves. The electron mobility is given by the following expression [29]:

$$\mu_{\rm e} = \frac{L^2 G_{\rm m}}{C_{\rm nw} V_{\rm ds}} \tag{1}$$

where L,  $G_{\rm m}$ ,  $C_{\rm nw}$  and  $V_{\rm ds}$  are, respectively, the channel length, the transconductance, the nanowire–oxide–back gate capacitance and the drain–source voltage, respectively. The transconductance,  $G_{\rm m} = dI_{\rm ds}/dV_{\rm g}$  is calculated as the fit of the slope of the transfer curve above the threshold voltage. The capacitance of the nanowire–dielectric–gate interface requires taking into account the device geometry. To estimate the capacitance we have considered two different analytical models and finite-element simulations for different geometries of the nanowire–oxide–gate interface [30–32].

Let us start first with the expression for the parallel-plate capacitor model:

$$C_{\rm nw}^{\rm p} = \frac{\varepsilon_0 \varepsilon_{\rm ox}}{t_{\rm ox}} WL \tag{2}$$

where *W* and  $t_{ox}$  are, respectively, the width of the SiNW channel and the thickness of the dielectric (figure 2(d)).

Let us now consider the capacitance of a cylindrical nanowire surrounded by a dielectric:

$$C_{\rm nw}^{\rm c} = \frac{2\pi\varepsilon_0\varepsilon_{\rm ox}}{\cosh^{-1}(t/R)}L\tag{3}$$

where *t* is the distance from the center of the wire to the bottom gate electrode ( $t = R + t_{ox}$ ).

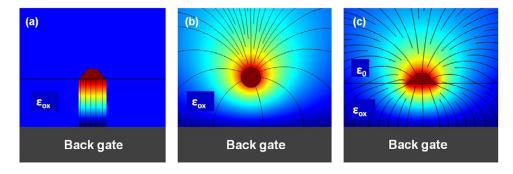

Figure 3 shows finite-element simulations (COMSOL Multiphysics) of the electric field lines for the two models described above and for a trapezoidal SiNW. The latter geometry is very close to that of the fabricated nanowires. The field lines of the cylindrical model are a better approximation to those of the trapezoidal SiNW than those of the parallel-plate model. Thus the cylindrical model is expected to give a better estimation of the capacitance than the planar model. This is verified by calculating the capacitance of a nanowire with a length and height respectively of 10.5  $\mu$ m and 32 nm. The value of the width is 85 and 20 nm for bottom and top sides (red section in figure 2(c)). For the parallel model the bottom side of the wire is taken. For the cylindrical model, the equivalent radius of the trapezoidal nanowire is obtained by matching the area of its section with that of a circle. For the above values we obtain for the parallel, cylindrical and trapezoidal cases, respectively, 0.2, 0.85 and 0.69 fF. Thus, the values of the capacitance of the fabricated SiNWs fall between the boundaries defined by the parallel-plate and cylindrical models, and, as expected, the cylindrical model gives a better estimation. The cylindrical model introduces a slight overestimation of the real value because it considers that a uniform dielectric surrounds the SiNW. However, in the fabricated nanowires a dielectric oxide isolates them from the gate electrode, but the top and lateral faces of the nanowire are surrounded by air which has a lower relative dielectric constant than the oxide ( $\varepsilon_{air} = 1$  compared to  $\varepsilon_{ox} = 3.9$  [31].

Once the capacitance has been estimated, the threshold voltage, the subthreshold swing and the electron mobility can be obtained from the transfer curves. The electrical characterization of the fabricated SiNW FETs was performed at room temperature with a setup consisting of a semiconductor characterization system (Keithley 4200) and a probe station (Everbeing EB 06, Taiwan).

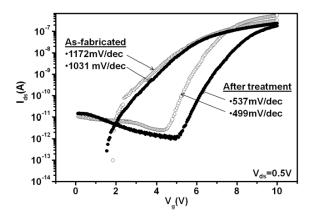

Figure 4 shows the transfer curves of two typical nanowire FETs fabricated, respectively, by oSPL and EBL. The mobility and the subthreshold swing are, respectively,  $102 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and  $1172 \text{ mV} \text{ dec}^{-1}$  for the oSPL device, and  $122 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and  $1031 \text{ mV} \text{ dec}^{-1}$  for the EBL device. Those values are considerably poorer than the ones reported for transistors fabricated by bottom-up and by top-down approaches (table 2). The fabrication of nanowire transistors by electron beam and scanning probe lithographies involves

**Figure 3.** Finite-element simulation of the field lines for different models of the nanowire–dielectric–gate interface. (a) Potential drop and electric field lines for a parallel-plate capacitor. (b) Potential drop and electric field lines for a cylindrical model. (c) Potential drop and electric field lines for a trapezoidal Si nanowire on top of a SiO<sub>2</sub> dielectric. The potential drop is illustrated by the color changes.

**Figure 4.** Transfer curves of the oSPL-fabricated (open circles) and EBL-fabricated (filled circles) SiNW transistors before and after applying a thermal pulse of  $300 \,^{\circ}$ C for  $30 \,^{\circ}$  n N<sub>2</sub>. After the thermal treatment the subthreshold swings of the two transistors are considerably steeper.

several steps of processing, which may adversely affect the electrical properties of the as-fabricated SiNW devices. For example, the irregularities at the metal–semiconductor contacts could create defects that, in turn, could produce a poor and unstable electrical response of the devices [33]. However, the anomalous behavior that is usually observed in as-fabricated devices can be significantly reduced or removed by annealing the devices. For this reason, we annealed the devices by applying thermal pulses of 300 °C with duration of 30 s under an N<sub>2</sub> atmosphere.

Before annealing, the devices fabricated by EBL show a slightly better performance—higher mobilities and lower SS—than the ones fabricated by oSPL. This is probably related to the fact that the process of fabrication by EBL involves one step less than that by oSPL. This might favor the fabrication of devices with fewer interfacial states and impurities. The properties of all the devices show a significant improvement after the thermal annealing. We also observe that the values of the mobility of the oSPL and EBL devices become very similar, with a relative difference of 4%. From this we conclude that the electrical properties are independent of the fabrication method. The remaining differences could be explained in terms of the differences in size and geometry.

Table 1. Electron mobility and SS values of SiNW transistors.

| oSPL                                                                                                                                                            | EBL                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| As-fabricated properties $\mu_e$ (cm² V <sup>-1</sup> s <sup>-1</sup> )82 <sup>a</sup> 217 <sup>b</sup> 102 <sup>c</sup> SS (mV dec <sup>-1</sup> )1172.        | $\begin{array}{c} As-fabricated \ properties \\ \mu_{e} \ (cm^{2} \ V^{-1} \ s^{-1}) \\ 101^{a} \\ 249^{b} \\ 122^{c} \\ SS \ (mV \ dec^{-1}) \\ 1031 \end{array}$ |

| After treatment properties<br>$\mu_{e} (cm^{2} V^{-1} s^{-1})$<br>167 <sup>a</sup><br>444 <sup>b</sup><br>208 <sup>c</sup><br>SS (mV dec <sup>-1</sup> )<br>499 | After treatment properties<br>$\mu_{e} (cm^{2} V^{-1} s^{-1})$<br>$179^{a}$<br>$413^{b}$<br>$200^{c}$<br>SS (mV dec <sup>-1</sup> )<br>537                         |

<sup>a</sup> Cylindric wire on plane model.

<sup>b</sup> Parallel-plate model.

<sup>c</sup> Trapezoidal model.

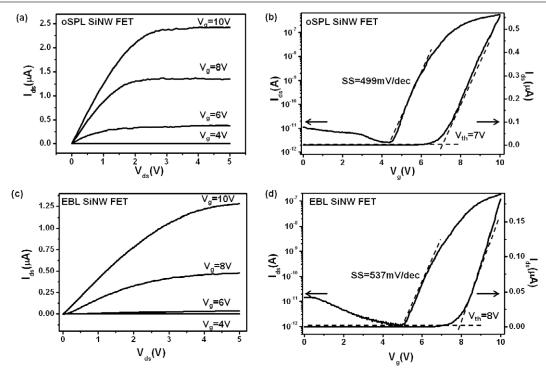

Figures 5(a) and (c) show the output characteristics of the two nanowire FETs shown in figure 4 after the thermal treatment. The curves show the linear as well as the saturation regimes and significant amplification behavior. Both devices are n-channel enhancement mode transistors, i.e., the transistors are off a zero gate voltage. The transfer characteristics in the linear region ( $V_{ds} = 0.5$  V) of the transistors on both linear and logarithmic scales are plotted in figures 5(b) and (d). The curves are very similar, with independence of the fabrication method. The threshold voltage for the oSPL transistor is 7 V while for the EBL transistor it is 8 V. The on/off ratio is about  $10^5$  in both cases. The electron mobilities, calculated according to equation (1) with  $C_{nw}$  estimated using the trapezoidal model, are  $208 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  for oSPL and  $200 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  for EBL. The small numerical differences are attributed to the different geometries of the fabricated SiNWs.

Table 1 presents the values of the mobility of the nanowire transistors calculated according to the different capacitor models presented in this work. The spread of values underlines the importance of considering the real geometry to estimate the device parameters. Those values are in agreement with what has been reported from other bottom-up and

**Figure 5.** Output and transfer curves of SiNW transistors. (a) Output curves of a device fabricated by oSPL. (b) Transfer curves of the device characterized in (a). (c) Output curves of a device fabricated by EBL. (d) Transfer curves of the device characterized in (c).

Table 2. SiNW features from different fabrication methods.

| Author [reference]     | Fabrication method                     | Gate dielectric                           | Channel<br>width (nm) | $\mu_{\rm e} \ ({\rm cm}^2  {\rm V}^{-1}  {\rm s}^{-1})$ | $SS (mV dec^{-1})$ |

|------------------------|----------------------------------------|-------------------------------------------|-----------------------|----------------------------------------------------------|--------------------|

| Zheng et al [39]       | Laser-assisted catalytic growth        | 60 nm ZnO <sub>2</sub>                    | 20                    | 270                                                      | 300                |

| Allen et al [40]       | VLS growth $+$ channel etching         | 200 nm Si <sub>3</sub> N <sub>4</sub>     | 50                    | 175                                                      | 600                |

| Chen <i>et al</i> [41] | Thermal oxidation                      | 13.6 nm SiO <sub>2</sub>                  | 48                    | 540                                                      | 60                 |

| Huang et al [9]        | Superlattice nanowire pattern transfer | $4 \text{ nm SiO}_2 + 6 \text{ nm HfO}_2$ | 10                    | 268                                                      | 168                |

| This work              | oSPL<br>EBL                            | 151 nm SiO <sub>2</sub>                   | 80<br>120             | 208<br>200                                               | 499<br>537         |

top-down fabrication approaches (table 2). The subthreshold swing values obtained from the transfer curves are 499 and 537 mV dec<sup>-1</sup> for oSPL and EBL, respectively (figure 5). Those values are about one order of magnitude higher than the ideal values for FETs at room temperature (60 mV dec<sup>-1</sup>). A theoretical calculation of the subthreshold swing SS is given by the expression [29]

$$SS = \ln 10 \left(\frac{kT}{q}\right) \left(1 + \frac{C_{\rm D}}{C'_{\rm nw}} + \frac{C_{\rm it}}{C'_{\rm nw}}\right) \tag{4}$$

where  $C_{\rm D}$  is the depletion layer capacitance,  $C_{\rm it}$  is the capacitance associated with the interface trap density and  $C'_{\rm nw}$  is the gate/channel capacitance in the subthreshold regime [29]. Using as a first approximation the parallel-plate model capacitance for  $C_{\rm D}$  and  $C_{\rm nw}$ , equation (4) reduces to  $SS \approx 60 \text{ mV dec}^{-1} (1+3t_{\rm ox}/t_{\rm Si}+C_{\rm it}/C_{\rm nw})$  [34]. Considering that in these devices  $t_{\rm ox} = 151 \text{ nm}$  and approximating  $t_{\rm Si}$  as the height of the wire  $\approx 50 \text{ nm}$  (full depletion), we would obtain, in the ideal case of zero interfacial traps, a value of about 600 mV dec<sup>-1</sup>, which is slightly higher than the values measured ( $\sim 500 \text{ mV dec}^{-1}$ ) after the thermal treatment.

However, the above approximation does not fully apply to these devices, because of geometrical considerations. First of all,  $C_{\rm D}$  is overestimated since the depletion length is comparable with the Debye length, which is of the order of 100 nm for the substrates used here. On the other hand, the value of  $C'_{nw}$  should take into account both the real geometry (trapezoidal) and the fact that, in the subthreshold regime, the nanowire-dielectric-back gate capacitance has an additional series term related to the depletion of the silicon gate electrode. Indeed, because of the relatively low doping, such a depletion length is comparable with the oxide thickness. As a consequence, the role of interfacial traps in affecting the subthreshold swing cannot be neglected, even after the thermal treatment. However, the observed decrease of the subthreshold swing indicates a reduction of the density of interfacial trap states. Furthermore, equation (4) indicates that the subthreshold swing would improve upon increase of  $C_{nw}$ , i.e. a reduction of the thickness of the dielectric. This is achieved by using alternative configurations like top gate [9, 35, 36], dual gate [37] and all-around gate [38]. However, those configurations impose a strong limitation on using the nanowire transistors as sensors. Indeed, the state-of-the-art sensors based on SiNW FETs [1, 7, 20] have values of subthreshold swing comparable with the ones presented in this work.

# 4. Conclusion

Oxidation scanning probe and electron beam lithographies have been applied to fabricate silicon nanowire field-effect transistors using the same wafer platform. This enables a direct comparison of the above top-down lithographies with respect to the nanowire fabrication process. Under similar conditions, scanning probe lithography provides nanowires of smaller channel widths than electron lithography. We have measured the electron mobility and the subthreshold swing of the nanowire transistors. The measured values are, respectively, about 200  $\text{cm}^2$  V<sup>-1</sup> s<sup>-1</sup> and about  $500 \text{ mV dec}^{-1}$ . The two lithographies provide similar values. Furthermore, the parameters of the nanowires fabricated by top-down approaches are similar to those obtained by bottomup lithographies. We remark that the subthreshold swing of the fabricated device is very close to its theoretical value. Here the values of the subthreshold swing were dominated by the thickness of the silicon dioxide dielectric layer. The agreement obtained validates the use of top-down lithographies for silicon nanowire fabrication. However, the as-fabricated devices show far from ideal transistor characteristics. Those features are easily removed by subjecting the nanowires to a thermal process.

### Acknowledgments

This work was funded by the Spanish Ministry of Science (MICINN) through MAT2009-08650 and the Comunidad de Madrid S2009/MAT-1467 and the European Commission FP7/2007-2013 under grant agreement No. 318804. MC acknowledges the program 'Juan de la Cierva' (MICINN).

#### References

- [1] Stern E, Klemic J F, Routenberg D A, Wyrembak P N, Turner-Evans D B, Hamilton A D, LaVan D A, Fahmy T M and Reed M A 2007 Label-free immunodetection with CMOS-compatible semiconducting nanowires *Nature* 445 519–22

- [2] Li Z, Chen Y, Li X, Kamins T I, Nauka K and Williams R S 2004 Sequence-specific label-free DNA sensors based on silicon nanowires *Nano Lett.* 4 245–7

- [3] Tian B, Cohen-Karni T, Qing Q, Duan X, Xie P and Lieber C M 2010 Three-dimensional, flexible nanoscale field-effect transistors as localized bioprobes *Science* 329 830–4

- [4] Kim W, Ng J K, Kunitake M E, Conklin B R and Yang P 2007 Interfacing silicon nanowires with mammalian cells J. Am. Chem. Soc. 129 7228–9

- [5] Tian R, Regonda S, Gao J, Liu Y and Hu W 2011 Ultrasensitive protein detection using lithographically defined Si multinanowire field effect transistors *Lab Chip* 11 1952–61

- [6] Chiesa M, Cárdenas P P, Otón F, Martínez J, Mas-Torrent M, García F, Alonso J C, Rovira C and Garcia R 2012

Detection of the early stage of recombinational DNA repair by silicon nanowire transistors *Nano Lett.* **12** 1275–81

- [7] Talin A A, Hunter L L, Léonard F and Rokad B 2006 Large area, dense silicon nanowire array chemical sensors *Appl. Phys. Lett.* 89 153102

- [8] McAlpine M C, Ahmad H, Wang D and Heath J R 2007 Highly ordered nanowire arrays on plastic substrates for ultrasensitive flexible chemical sensors *Nature Mater*. 6 379–84

- [9] Huang R-G, Tham D, Wang D and Heath J R 2011 High performance ring oscillators from 10 nm wide silicon nanowire field-effect transistors *Nano Res.* 4 1005–12

- [10] Gil-Santos E, Ramos D, Martínez J, Fernández-Regúlez M, García R, San Paulo A, Calleja M and Tamayo J 2010 Nanomechanical mass sensing and stiffness spectrometry based on two-dimensional vibrations of resonant nanowires *Nature Nanotechnol.* 5 641–5

- [11] Yang P, Yan R and Fardy M 2010 Semiconductor nanowire: what's next? Nano Lett. 10 1529–36

- [12] Stelzner T, Pietsch M, Andrä G, Falk F, Ose E and Christiansen S 2008 Silicon nanowire-based solar cells *Nanotechnology* 19 295203

- [13] Qing Q, Pal S K, Tian B, Duan X, Timko B P, Cohen-Karni T, Murthy V N and Lieber C M 2010 Nanowire transistor arrays for mapping neural circuits in acute brain slices *Proc. Natl Acad. Sci. USA* 107 1882–7

- [14] Kwiat M et al 2012 Highly ordered large-scale neuronal networks of individual cells—toward single cell to 3D nanowire intracellular interfaces ACS Appl. Mater. Interfaces 4 3542–9

- [15] Shao M, Ma D D D and Lee S-T 2010 Silicon nanowires—synthesis, properties, and applications *Eur. J. Inorg. Chem.* 27 4264–78

- [16] Trivedi K, Yuk H, Floresca H C, Kim M J and Hu W 2011 Quantum confinement induced performance enhancement in sub-5-nm lithographic Si nanowire transistors *Nano Lett.* 11 1412–7

- [17] Morton K J, Nieberg G, Bai S and Chou S Y 2008 Wafer-scale patterning of sub-40 nm diameter and high aspect ratio (>50:1) silicon pillar arrays by nanoimprint and etching *Nanotechnology* 19 345301

- [18] Martínez R V, Martínez J and Garcia R 2010 Silicon nanowire circuits fabricated by AFM oxidation nanolithography *Nanotechnology* 21 245301

- [19] Martínez J, Martínez R V and Garcia R 2008 Silicon nanowire transistors with a channel width of 4 nm fabricated by atomic force microscope nanolithography *Nano Lett.* 8 3636–9

- [20] Koo S-M, Edelstein M D, Li Q, Richter C A and Vogel E M 2005 Silicon nanowires as enhancement-mode Schottky barrier field-effect transistors *Nanotechnology* 16 1482–5

- [21] Knoch J and Appenzeller J 2002 Impact of the channel thickness on the performance of Schottky barrier metal–oxide–semiconductor field-effect transistors Appl. Phys. Lett. 81 3082–4

- [22] Léonard F and Talin A A 2011 Electrical contacts to one- and two-dimensional nanomaterials *Nature Nanotechnol*.

6 773–83

- [23] Heinzig A, Slesazeck S, Kreupl F, Mikolajick T and Weber W M 2012 Reconfigurable silicon nanowire transistors *Nano Lett.* 12 119–24

- [24] Garcia R, Martinez R V and Martinez J 2006 Nanochemistry and scanning probe nanolithographies *Chem. Soc. Rev.* 35 29–38

- [25] Knoll A W, Pires D, Coulembier O, Dubois P, Hedrick J L, Frommer J and Duerig U 2010 Probe-based 3D nanolithography using self-amplified depolymerization polymers Adv. Mater. 22 3361–5

- [26] Grigorescu A E and Hagen C W 2009 Resists for sub-20-nm electron beam lithography with a focus on HSQ: state of the art *Nanotechnology* 20 292001

- [27] García R, Calleja M and Pérez-Murano F 1998 Local oxidation of silicon surfaces by dynamic force microscopy: nanofabrication and water bridge formation *Appl. Phys. Lett.* 72 2295–7

- [28] Calleja M, Tello M and García R 2002 Size determination of field-induced water menisci in noncontact atomic force microscopy J. Appl. Phys. 92 5539–42

- [29] Sze S M and Ng K K 2006 *Physics of Semiconductor Devices* 3rd edn (Hoboken, NJ: Wiley)

- [30] Wunnicke O 2006 Gate capacitance of back-gated nanowire field-effect transistors Appl. Phys. Lett. 89 083102

- [31] Khanal D R and Wu J 2007 Gate coupling and charge distribution in nanowire field effect transistors *Nano Lett.* 7 2778–83 083102

- [32] Hayden O, Björk M T, Schmid H, Riel H, Drechsler U, Karg S F, Lörtscher E and Riess W 2007 Fully depleted nanowire field-effect transistor in inversion mode *Small* 3 230–4

- [33] Rurali R 2010 Colloquium: structural, electronic, and transport properties of silicon nanowires *Rev. Mod. Phys.* 82 427–49

- [34] Black C T 2005 Self-aligned self assembly of multi-nanowire silicon field effect transistors *Appl. Phys. Lett.* 87 163116

- [35] Li Q, Zhu X, Yang Y, Ioannou D E, Xiong H D, Kwon D-W, Suehle J S and Richter C A 2009 The large-scale integration of high-performance silicon nanowire field effect transistors *Nanotechnology* 20 415202

- [36] Frei J et al 2004 Body effect in tri- and pi-gate SOI MOSFETs IEEE Electron Device Lett. 25 813–5

- [37] Koo S-M, Li Q, Edelstein M D, Richter C A and Vogel E M 2005 Enhanced channel modulation in dual-gated silicon nanowire transistors *Nano Lett.* 5 2519–23

- [38] Björk M T, Hayden O, Schmid H, Riel H and Riess W 2007 Vertical surround-gated silicon nanowire impact ionization field-effect transistors *Appl. Phys. Lett.* **90** 142110

- [39] Zheng G, Lu W, Jin S and Lieber C M 2004 Synthesis and fabrication of high-performance n-type silicon nanowire transistors Adv. Mater. 16 1890–3

- [40] Allen J E, Hemesath E R and Lauhon L J 2009 Scanning photocurrent microscopy analysis of Si nanowire field-effect transistors fabricated by surface etching of the channel *Nano Lett.* 9 1903–8

- [41] Chen J, Saraya T, Miyaji K, Shimizu K and Hiramoto T 2009 Electron mobility in silicon gate-all-around [100]- and [110]-directed nanowire metal–oxide–semiconductor field-effect transistor on (100)-oriented silicon-on-insulator substrate extracted by improved split capacitance–voltage method Japan. J. Appl. Phys. 48 011205